汽车零部件EMC整改案例系列专题-某车机产品高速DDR时钟信号PCB布线EMI问题整改分析案例

某车机产品高速DDR时钟信号

布线不当引起辐射骚扰问题的整改分析案例

单位名称:深圳市赛盛技术有限公司

作者:夕阳西下 时间:2019-12-12

一、 现象描述

1. 产品信息

某车机产品,其主要功能特性为利用车载GPS(全球定位系统)配合电子地图来进行地图导向,同时兼具音视频播放、收音接收、蓝牙免提、触摸屏、智能轨迹倒车、胎压检测功能等后台控制功能。

图 1 产品图示

其接口特性如下:

接口名称 | 接口数量 | 接口类型 | 信号速率 | 电缆类型 | 备注 |

USB | 1 | 480MHz | 非屏蔽 | ||

Radio-ANT | 1 | 522-1600k/87.5-108M | 屏蔽 | AM/FM | |

Speaker | 1 | 1KHz | 屏蔽 | ||

RVC | 1 | 6.5MHz | 非屏蔽 | CVBS | |

BAT | 1 | DC | 非屏蔽 |

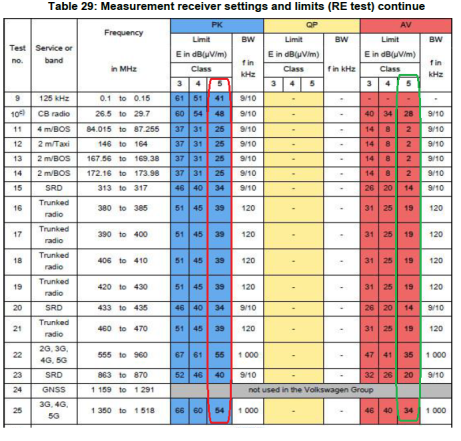

2. 试验要求

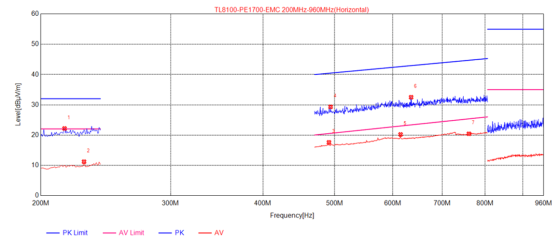

按照大众车厂汽车电子零部件电磁兼容测试标准TL-81000-2016中的要求进行测试,其中辐射骚扰测试项目要求满足Class 5 。测试频段要求100kHz-18GHz,测试检波方式为PK与AV,QP不做要求。

3. 问题描述

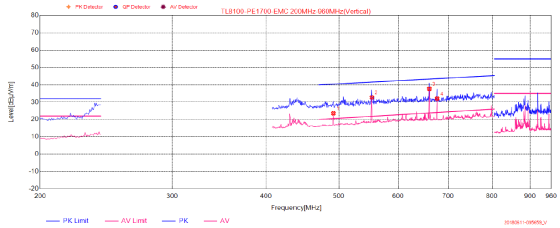

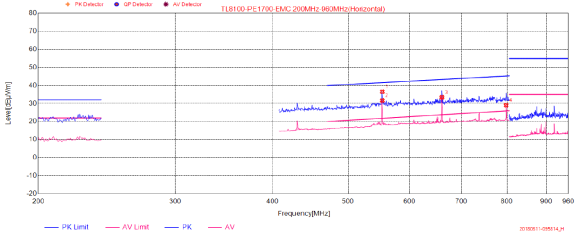

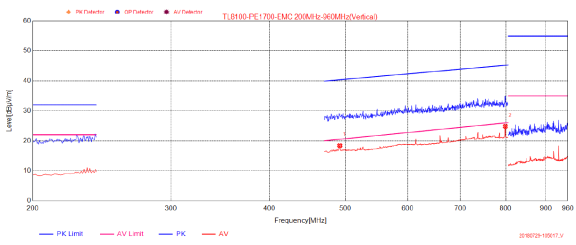

产品进行辐射骚扰测试项目时发现在 200MHz~1GHz的测试频段AV检波严重超标,其中频点660MHz超标10dB。

图 2 天线垂直方向超标情况

图 3 天线水平方向超标情况

二、 原因分析

所有电磁兼容问题的产生必须存在三个要素:干扰源、耦合路径和敏感设备。因此要解决电磁兼容问题只需从这三个要素入手,消除其中某一要素,便可解决电磁兼容问题。

结合产品的RE初始测试结果、产品各功能模块的工作频率,对测试结果频谱图形进行分析,超标频点660MHz的频谱图形特性类型为窄带单支噪声,可能存在的噪声源为CPU时钟电路、DDR时钟电路、晶振时钟电路;可能存在的辐射路径为结构面板搭接缝隙、连接器开孔、对外电缆。

问题频点 | 最大超标值 | 频谱形态 | 噪声源分析 | 辐射路径分析 |

660MHz | 10dB | 单支时钟 | CPU时钟电路、DDR时钟电路、晶振时钟电路 | 结构缝隙、开孔、电缆 |

由于高频辐射路径的分析比较复杂,因此下面我们主要分析噪声源头;

1. 噪声源头的查找及确认;

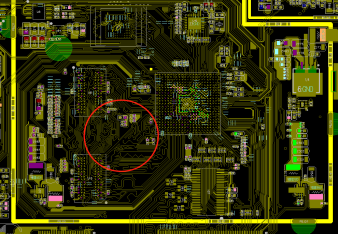

通过圆环型近场探头探视其主控板上各功能模块电路和晶振电路,确定该频段噪声电路为DDR电路;

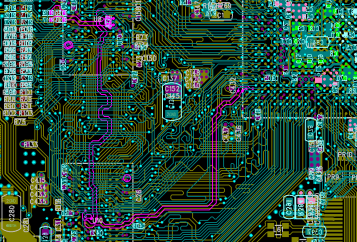

图 4 圆环探头近场定位的噪声区域

通过探针型近场探头探视DDR电路上各信号点,确定该频段噪声源头为DDR时钟差分信号对CKL、CKN;

图 5 探针探头近场定位的噪声信号

2. PCB高速信号布线不当对EMI的影响

差分时钟是DDR的一个非常重要的设计,是对触发时钟进行校准,主要原因是DDR数据的双沿采样。由于数据是在时钟的上下沿触发,传输周期缩短了一半,但其工作速率的增加也带来了严重的EMI问题。检视DDR时钟差分对的PCB布线,发现其存在布线过长、换层过孔未做伴地过孔处理。

下面分析这两个时钟信号布线缺陷对EMI的具体影响。

(1) 高速时钟信号布线距离过长对EMI的影响

电子产品单板PCB对外产生的干扰可分为共模与差模干扰(本案例的问题主要由共模干扰引起),产生干扰的原因是单板PCB上存在着对应的共模(CM)干扰电流和差模(DM)干扰电流。单板上产生的干扰以传导或辐射的方式对外形成发射,从而导致产品EMI问题。

产品对外的干扰多以共模为主,要精确计算PCB对外的辐射很难,业界通常根据PCB中的差模电流和共模电流近似的辐射天线模型来计算对外干扰的场强大小;计算共模辐射强度时,可以近似等效为单极子天线模型,也称为棒天线模型。

单极子天线模型的辐射强度由下式计算:

E=12.6*10-7fIL/r

其中:

E:电场强度(V/m)

f :电流的频率(MHz)

L:电缆/布线的长度(m)

I :电流的强度(mA)

r :测试点到电流环路的距离(m)

由公式可知,共模干扰的远场值与频率、共模电流值、等效天线的长度直接相关,在PCB设计中需要尽可能的减小激励电流值与等效模型中的天线长度,从而达到减小PCB共模辐射的目的。

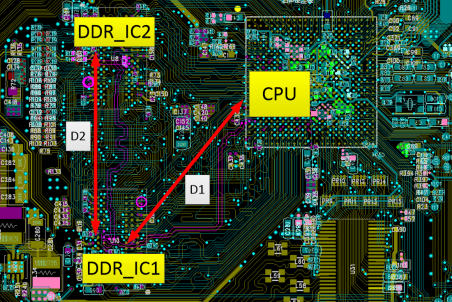

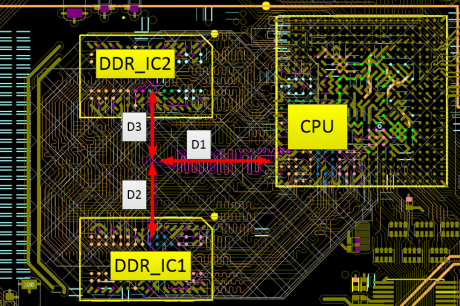

图 6 布线路径及其距离分析

检视产品PCB可知,CPU、DDR_IC1、DDR_IC2三者之间通过差分时钟信号对CK、CKN进行通讯;CPU至IC1的布线距离约为D1(0.03m),IC1至IC2的布线距离约为D2(0.03m),而CPU至IC2的布线距离约为D1+D2(0.06m)。

将所有已知条件代入上述公式(E=12.6*10-7fIL/r),其中f为660MHz,I为20mA,L为0.06m,r为1m;可知该DDR差分信号对的最大对外辐射电场强度达到64dBuV/m;此电场强度已远远超过TL 81000标准在该频段400MHz~1GHz所规定的限值40dBuV/m(未考虑产品壳体屏蔽等其他措施的情况下)。

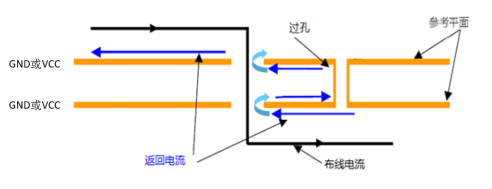

(2) 高速时钟信号换层过孔时未做伴地过孔处理对EMI的影响;

检视产品PCB可知,该DDR差分时钟对CK、CKN布线时不可避免的存在换层过孔的现象,但在其换层过孔时却未在过孔附近做伴地过孔处理;此时,时钟信号跨越了两个不同参考平面导致信号回流不连续,从而产生严重的EMI问题。

图 7 布线换层过孔电流路径分析

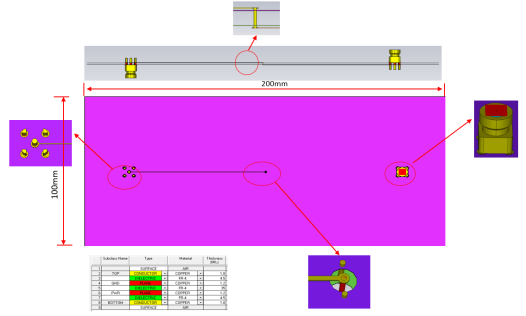

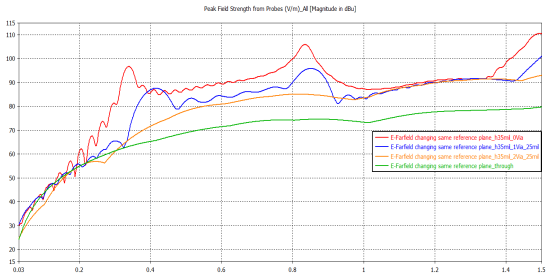

模拟产品单板的特征情景:在仿真软件上设置4层板、尺寸为200mm * 100mm、参考面间距35mil、表层和底层走线长度个75mm、走线带宽7mil、走线阻抗控制为50Ω的条件;通过不加伴地孔、增加一个伴地孔和增加两个伴地孔等多种情景对其进行仿真分析。

图 8 仿真条件设定

图 9 换层过孔的信号在多种情景下的远场辐射特性分析

由远场的仿真分析图可知:在400MHz~1GHz频段,DDR时钟信号穿层过孔时增加两个伴地过孔的情景(橙色线)比不加伴地过孔的情景(红色线)改善了10dB以上。

三、 措施与方案

1. 优化CLK时钟信号布线长度。

调整CPU至DDR_IC2之间的布线路径,缩短两者间的布线距离。

图 10 改板后的PCB图

调整后的PCB图中,CPU至IC1、CPU至IC2之间的距离均为0.03m;

将所有已知条件代入上述公式(E=12.6*10-7fIL/r), 其中f为660MHz,I为20mA,L为0.03m,r为1m;可知该DDR差分信号的最大对外辐射电场强度为54dBuV/m;说明按照理论计算,改板后比改板前优化了10dB(改板前为64dBuV/m)。

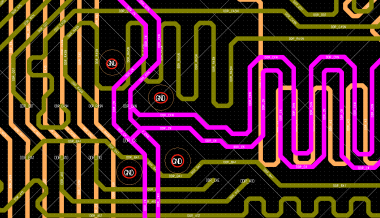

2. 在CLK换成过孔位置附近打相应的地过孔

按照上述仿真分析结果指导,在DDR时钟信号换层过孔附近打上两个相邻伴地过孔。

图 11 改板后的PCB图

四、 试验结果

将改板后的产品在同等条件下进行RE测试验证,在频段200MHz~1GHz范围内大余量通过,时钟窄带信号干扰消失。

图 12 改板后天线水平方向PASS情况

图 13 改板后天线垂直方向PASS情况

五、 经验分享

1. 高速时钟走线尽可能的避免在PCB表层长距离走线,表层走线构成的单极子天线辐射模型会加大时钟的高次谐波辐射值。

2. 高速信号特别是高速时钟差分信号除了要注意信号线走线短,与完整的平面相邻外,还需注意换层走线问题。

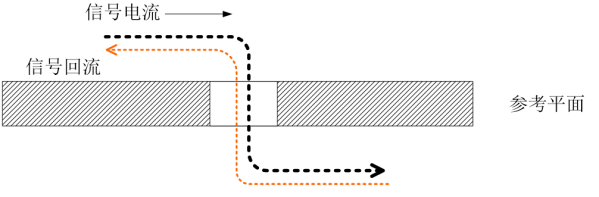

3. 高速信号线换层走线,应以同一层参考平面为中心,保持回流电流在同一平面层上流动,保证电流的连续性。如下图所示,对于高频电流,由于导体的趋肤效应,回流电流是在参考平面的两个表面流动的。

图 14 信号线以同一层参考平面为中心换层

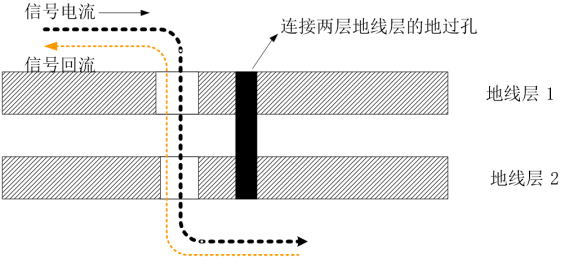

4. 若高速信号线穿过两层地平面,需要在信号线换层的过孔附近至少设置一个(最好是两个)桥接地过孔,将两层地平面连接起来,以保证地平面上回流电流的连续性,如下图所示:

图 15 信号线在两个地平面之间换层